Intel Xeon Processor Scalable Family Increases EDA Throughput

|

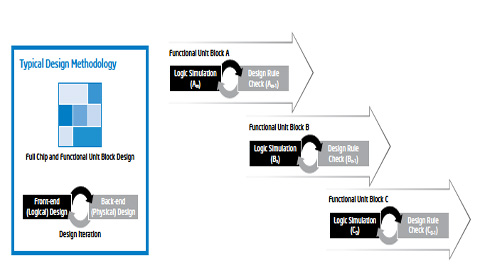

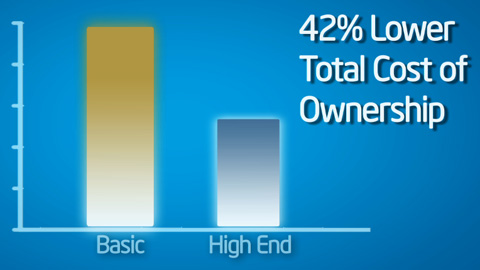

IT Best Practices: Intel’s silicon design engineers need significant increases in computing capacity—both on their workstations and on data center servers—to deliver each new generation of silicon chips. To meet those requirements, Intel IT conducts ongoing throughput performance tests, using [See the full post…] |

|

|